# Lecture Notes in Computer Science Edited by G. Goos, J. Hartmanis and J. van Leeuwen

1667

# Springer Berlin

Berlin

Heidelberg

New York

Barcelona

Hong Kong

London

Milan

Paris

Singapore

Tokyo

Jan Hlavička Erik Maehle András Pataricza (Eds.)

# Dependable Computing – EDCC-3

Third European Dependable Computing Conference Prague, Czech Republic, September 15-17, 1999 Proceedings

#### Series Editors

Gerhard Goos, Karlsruhe University, Germany Juris Hartmanis, Cornell University, NY, USA Jan van Leeuwen, Utrecht University, The Netherlands

#### Volume Editors

Jan Hlavička

Czech Technical University in Prague

Department of Computer Science and Engineering

Karlovo nam 13, CZ-12135 Prague 2, Czech Republic

E-mail: hlavicka@cslab.felk.cvut.cz

Erik Maehle

Medizinische Universität zu Lübeck, Institut für Technische Informatik

Ratzeburger Allee 160, 23538 Lübeck, Germany

E-mail: maehle@iti.mu-luebeck.de

András Pataricza

Technical University of Budapest

Department of Measurement and Information Systems

Pázmány P. sétány 1/d, H-1521 Budapest, Hungary

E-mail: pataric@mit.bme.hu

Cataloging-in-Publication data applied for

Die Deutsche Bibliothek - CIP-Einheitsaufnahme

Dependable computing: proceedings/EDCC-3, Third European Dependable Computing

Conference, Prague, Czech Republic, September 15 - 17, 1999. Jan Hlavicka ...

(ed.). - Berlin; Heidelberg; New York; Barcelona; Hong Kong; London;

Milan; Paris; Singapore; Tokyo: Springer, 1999 (Lecture notes in computer science; Vol. 1667)

ISBN 3-540-66483-1

CR Subject Classification (1998): B.1.3, B.2.3, B.3.4, B.4.5, C.3-4, D.2.4, D.2.8,

D.4.5, E.4, J.7

ISSN 0302-9743

ISBN 3-540-66483-1 Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

© Springer-Verlag Berlin Heidelberg 1999 Printed in Germany

Typesetting: Camera-ready by author

SPIN: 10705369 06/3142 – 5 4 3 2 1 0 Printed on acid-free paper

#### **Foreword**

The idea of creating the European Dependable Computing Conference (EDCC) was born at the moment when the Iron Curtain fell. A group of enthusiasts, who were previously involved in research and teaching in the field of fault-tolerant computing in different European countries, agreed that there is no longer any point in keeping previously independent activities apart and created a steering committee which took the responsibility for preparing the EDCC calendar and appointing the chairs for the individual conferences. There is no single European or global professional organization that took over the responsibility for this conference, but there are three national interest groups that sent delegates to the steering committee and support its activities, especially by promoting the conference materials. As can be seen from these materials, they are the SEE Working Group "Dependable Computing" (which is a successor organization of AFCET) in France, the GI/ITG/GMA Technical Committee on Dependability and Fault Tolerance in Germany, and the AICA Working Group "Dependability of Computer Systems" in Italy. In addition, committees of several global professional organizations, such as IEEE and IFIP, support this conference.

Prague has been selected as a conference venue for several reasons. It is an easily accessible location that may attract many visitors by its beauty and that has a tradition in organizing international events of this kind (one of the last FTSD conferences took place here). However, there is one other fact, which may not be known by the general public, that makes Prague a special place for organizing a conference on dependable computing. It was here in 1957 that the first fault-tolerant computer in the world was set into operation. It was a relay computer SAPO that had three ALUs working in the TMR mode. The machine was designed by Professor Antonin Svoboda at the Institute of Mathematical Machines, which he founded and managed for some time. Thus this conference can be seen as a way in which the Czech Technical University pays tribute to this great man of science.

Preparing an international conference is always a question of teamwork and I was lucky to have the opportunity to work with an excellent team. Availability of modern means of communication, especially the Internet, made it relatively easy to form such a team across several borders and to coordinate its activities during the last two years. It is impossible to name all those who contributed to the success of the EDCC-3. Let me mention at least some of them.

The main load of responsibility naturally lay on the shoulders of the conference chairs. Each of them, being responsible for his or her sector, invested much effort and did an excellent job. In addition to three face-to-face meetings they exchanged thousands of e-mails, phone calls, and written messages while fine-tuning the final image of the conference. At this point it should be mentioned that each of the program co-chairs established a team within his own workplace and received very important support from his host institution. These institutions, namely, the Medical University of Lübeck in Germany and the Technical University of Budapest in Hungary, deserve our sincere

thanks, because without their generous support the conference would hardly be what it is now.

The Czech Technical University, as the main organizer of this year's conference, offered us the services of its CTU Congress Agency. In cooperation with the finance and local arrangements chair, this agency arranged the conference venue, accommodations, and social program, and handled registration. Its staff worked very efficiently and helped to keep the conference budget within reasonable limits.

The list of those who contributed to the success of the conference would be incomplete without our sponsors. Six local companies responded to our call and helped us to create a fund from which we could finance the participation of students and active participants from countries having restricted access to freely convertible currency.

Finally, I can conclude that it was a pleasure to work with people who are so dedicated to their jobs and so dependable (no pun intended!) in their activities. I can only wish that the conference participants enjoy both the technical and social program of the conference as much as we enjoyed preparing it.

Prague, June 1999

Jan Hlavička EDCC-3 General Chair

### **Preface**

The Third European Dependable Computing Conference can already rely on the traditions defined by the previous two conferences in this series. EDCC-1 was held in Berlin, on 4-6 October, 1994; and EDCC-2 in Taormina, on 2-4 October, 1996.

Originating from two former conference series – the "International Conference on Fault-Tolerant Computing Systems" and the "International Conference on Fault-Tolerant Systems and Diagnostics," EDCC was one of the pioneers in the unification of scientific life in the two parts of Europe after the political barriers had vanished.

The main focus of the conference reflects the changes in the rapidly growing and ever more extensive field of computer applications. In addition to the traditional topics in dependable computing, such as testing, general hardware and software reliability, safety and security, the rapid development of the infrastructural background of research and of practical applications triggered a shift in the main topics during the last decade.

The growing importance of the field of dependability both in technology and in everyday life is prominently indicated by the fact that the European Community defined, in its 1999 Workprogramme of the 5th Framework Programme on Information Society Technologies, an autonomous Cross-Programme Action under the title "Dependability in services and technologies."

This action defines the main objective of forthcoming European research: "To develop technologies, methods and tools that will meet the emerging generic dependability requirements in the information society, stemming both from the ubiquity and volume of embedded and networked systems and services as well as from the global and complex nature of large-scale information and communication infrastructures, from citizens (especially with respect to enhancing privacy), administrations and business in terms of technologies (hardware and software), tools, systems, applications and services. The work must reflect the wide scalability and heterogeneity of requirements and operating environments. There will be an emphasis on risk and incident management tools as well as on privacy enhancing technologies. The scope includes self-monitoring, self-healing infrastructures and services."

We hope that our conference will contribute to these goals. Fortunately, the conference received a large number of submissions. All papers were sent to four reviewers, two program committee (PC) or steering committee members and two external experts. No paper was processed with less than three reviews returned to the PC.

The PC held a two-day meeting in Budapest, as the final phase of decision making, after receiving the reviews. The basic principle adopted by the PC was to "discuss until consensus is reached." According to this principle, whenever a remarkable difference was detected between the reviews, a new PC member was assigned to consider the paper and all previous reviews. If there was a difference of opinion between the PC members familiar with the candidate's paper, a new PC member was assigned to lead a consensus discussion among them. Any PC member with a conflict of interest was excluded from the discussion of the corresponding paper. Finally, after four rounds of discussion, the

PC selected 26 papers (3 of them for the industrial track) out of the 71 submissions from 25 countries.

In order to facilitate fast feedback from the international scientific community, the organizers decided to follow the successful pattern of other conferences, such as that of IEEE FTCS, and introduced the Fast Abstract Session for the presentation of results from work in progress. Twenty submissions were selected by the program co-chairs for presentation in this form.

In addition to our regular scientific program, a Dinner Speech is delivered by Prof. Dr. Winfried Görke from the University of Karlsruhe, Germany. Prof. Görke is a very well-known European pioneer in the fields of testing and fault-tolerant computing. He played an important and outstanding role in establishing connections between researchers in Western and Eastern Europe in the difficult times of the Iron Curtain and is one of the founders of the German Special Interest Group of Fault-Tolerant Computing. In his speech in the historic environment of the Bethlehem's Chapel in Prague he talks about the history of fault-tolerant computing in Europe.

The Conference was organized by

- SEE Working Group "Dependable Computing," France

- GI/ITG/GMA TC on Dependability and Fault Tolerance, Germany

- AICA Working Group "Dependability of Computer Systems," Italy

under the auspices of the Council of European Professional Informatics Societies (CEPIS), and in cooperation with

- Czech Technical University in Prague

- IFIP Working Group 10.4 "Dependable Computing and Fault-Tolerance"

- IEEE TC on Fault-Tolerant Computing

- EWICS Technical Committee on Safety, Reliability and Security (TC7).

The organizers gratefully acknowledge the help of all reviewers, the staff at the Medical University of Lübeck, the Czech Technical University in Prague and the Technical University of Budapest. The organizers express their thanks to Ram Chillarege at IBM for supporting the review process by making available to them the electronic reviewing system originally prepared for FTCS-28.

A few days before our PC meeting the sad news reached us that Dr. Flaviu Cristian from UC San Diego, USA, had passed away on Tuesday, April 27, after a long and courageous battle with cancer. Being a leading expert in the field of distributed fault-tolerant systems we had also asked him to review some papers, which he, however, could not complete because of his illness. Flaviu Cristian was born in Romania in 1951, and moved to France in 1971 to study computer science. He received his Ph. D. from the University of Grenoble, France in 1979, where he carried out research in operating systems and programming methodology. He went on to the University of Newcastle upon Tyne, UK and worked in the area of specification, design, and verification of fault-tolerant software. In 1982 he joined IBM Almaden Research Center. While at IBM, he received the Corporate Award, IBM's highest technical award, for his work on the Advanced Automation System for air traffic control. Subsequently he joined UC San

Diego as professor in the Department of Computer Science and Engineering in 1991. He was elected a Fellow of the Institute for Electrical and Electronic Engineers in 1998 for his contributions to the theory and practice of dependable systems. Flaviu Cristian's work on the design and analysis of fault-tolerant distributed systems was fundamental, and he was widely regarded as one of the technical leaders in his field. The impact of his work was felt both in the theory and in the practice of fault-tolerance.

We express our gratitude to Springer Verlag for publishing the proceedings of the conference. This year two important changes were made for additional distribution of information:

- Springer will offer, in addition to the print version, an electronic form of the proceedings.

- Similarly, the final text of the fast abstracts will be made available via the web at the URL: http://www.inf.mit.bme.hu/edcc3/.

July 1999

András Pataricza, Erik Maehle EDCC-3 Program Co-Chairs

# **Organizing Committee**

#### **General Chair**

Jan Hlavička Czech Technical University Prague, Czech Republic

#### **Program Co-Chairs**

Erik Maehle Medical University of Lübeck Germany

Finance and Local Arrangements Chair

Hana Kubátová Czech Technical University Prague, Czech Republic András Pataricza Technical University of Budapest Hungary

## **Publicity Chair**

Karl-Erwin Grosspietsch German National Research Center for Information Technology (GMD) St. Augustin, Germany

#### **International Liaison Chairs**

North America: Dimiter Avresky Boston University USA Asia: Takashi Nanya University of Tokyo Japan

# **EDCC Steering Committee**

Algirdas Avizienis, USA Mario Dal Cin, Germany Jan Hlavička, Czech Republic Andrzej Hławiczka, Poland Hermann Kopetz, Austria Jean-Claude Laprie, France Brian Randell, UK Ernst Schmitter, Germany Luca Simoncini, Italy Pascale Thévenod-Fosse, France Jan Torin, Sweden Raimund Ubar, Estonia

## **Program Committee**

Arturo Amendola, Italy

Jean Arlat, France

Andrea Bondavalli, Italy

Bernard Courtois, France

Pierre Jacques Courtois, Belgium

Klaus Echtle, Germany

Bernd Eschermann, Switzerland

Joan Figueras, Spain

Elena Gramatová, Slovakia

Bjarne Helvik, Norway

Johan Karlsson, Sweden

Hans Kerkhoff, Netherlands

Henryk Krawczyk, Poland

Piero Maestrini, Italy

István Majzik, Hungary

Miroslaw Malek, Germany

Gilles Muller, France

Edgar Nett, Germany

Dimitris Nikolos, Greece

Franc Novak, Slovenia

Ondřej Novák, Czech Republic

David Powell, France

Andrew Richardson, UK

André Schiper, Switzerland

Erwin Schoitsch, Austria

João Gabriel Silva, Portugal

Egor S. Sogomonyan, Russia

Janusz Sosnowski, Poland

Bernd Straube, Germany

Paulo Verissimo, Portugal

#### **External Referees**

Anceaume, E. Kalbarczyk, Z. Raik, J. Avresky, D. Kanoun, K. Raynal, M. Bartha, T. Karl, H. Rodrígues, L. Belli, F. Kermarrec, A.M. Romanovski, A. Boichat, R. Kopetz, H. Rufino, J. Chessa, S. Korousic-Seljak, B. Santi. P. Crouzet, Y. Krasniewski, A. Schlichting, R. Csertán, Gy. Kropf, T. Schneeweiss, W. Deconinck, G. Landrault, C. Selényi, E. DiGiandomenico, F. Latella, D. Silc, J. Ma, Y. Silva, L.M. Dilger, E. Draber, S. Madeira, H. Simon, Gy. Elnozahy, E.N. Masum, A. Skavhaug, A. Ezhilchelvan, P. Mock, M. Sobe, P. Fabre, J.C. Mostefaoui, A. Stalhane, T. Fantechi, A. Mura, I. Sziray, J. Fetzer, C. Nicolaïdis, M. Tangelder, R. Geisselhardt, W. Noyes, D. Tarnay, K. Gil, P. Obelöer, W. Telek, M. Gnesi, S. Pedone, F. Urbán, P. Peng, Z. Görke, W. Vergos, H. Gössel, M. Petri, A. Jr. Vernadat, F. Grandoni, F. Petri, S. Vierhaus, T. Voges, U. Grosspietsch, K.-E. Piestrak, S. Hazelhurst, S. Polze, A. von Henke, F.

Puaut, I.

Racek, S.

Puschner, P.

Waeselynck, H.

Yarmolik, V.N.

Werner, M.

Ibach, P.

Kaiser, J.

Kaaniche, M.

# **Table of Contents**

| Keynote Speech                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------|

| Reliable and Secure Operation of Smart Cards                                                                                       |

| Session 1: Dependability Modelling Chair: Jean-Claude Laprie, LAAS-CNRS, Toulouse, France                                          |

| Dependability Modelling and Sensitivity Analysis of Scheduled Maintenance Systems                                                  |

| Evaluation of Video Communication over Packet Switching Networks                                                                   |

| Dependability Evaluation of a Distributed Shared Memory Multiprocessor System 42 M. Rabah, K. Kanoun (LAAS-CNRS, Toulouse, France) |

| Session 2a: Panel  Moderator: Fevzi Belli, University of Paderborn, Germany                                                        |

| Software Reliability Engineering – Risk Management for the New Millenium 63 F. Belli (University of Paderborn, Germany)            |

| Session 2b: Fast Abstracts Chair: Dimiter Avresky, Boston University, USA                                                          |

| List of Fast Abstracts                                                                                                             |

| Session 3: Protocols Chair: István Majzik, Technical University of Budapest, Hungary                                               |

| Muteness Failure Detectors: Specification and Implementation                                                                       |

| A Fault Tolerant Clock Synchronization Algorithm for Systems with Low-Precision Oscillators                                        |

| Avoiding Malicious Byzantine Faults by a New Signature Generation Technique . 106  K. Echtle (University of Essen, Germany)        |

| An Experimental Evaluation of Coordinated Checkpointing in a Parallel Machine 124<br>L.M. Silva, J.G. Silva (Universidade de Coimbra, Portugal)                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Session 4: Fault Injection 1 Chair: Janusz Sosnowski, Warsaw University of Technology, Poland                                                                                                                  |

| MAFALDA: Microkernel Assessment by Fault Injection and Design Aid 143<br>M. Rodríguez, F. Salles, JC. Fabre, J. Arlat (LAAS-CNRS, Toulouse, France)                                                            |

| Assessing Error Detection Coverage by Simulated Fault Injection                                                                                                                                                |

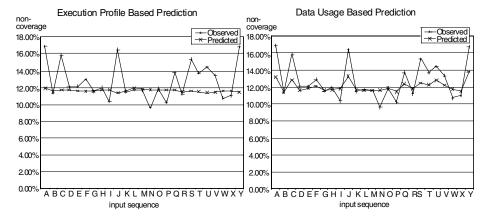

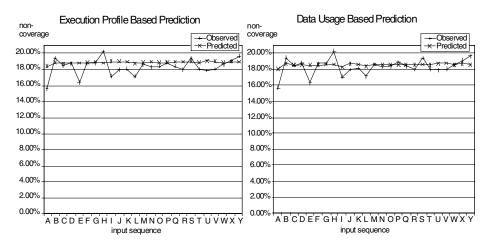

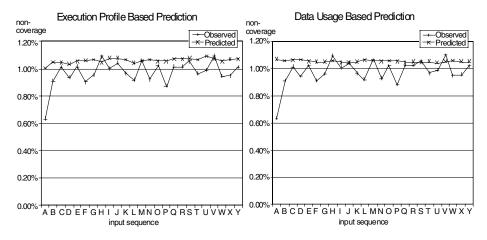

| Considering Workload Input Variations in Error Coverage Estimation 171<br>P. Folkesson, J. Karlsson (Chalmers University of Technology, Göteborg, Sweden)                                                      |

| Session 5: Fault Injection 2 Chair: David Powell, LAAS-CNRS, Toulouse, France                                                                                                                                  |

| Fault Injection into VHDL Models: Experimental Validation of a Fault-Tolerant Microcomputer System                                                                                                             |

| Can Software Implemented Fault-Injection be Used on Real-Time Systems? 209<br>J.C. Cunha (Instituto Superior de Engenharia de Coimbra, Portugal),<br>M.Z. Rela, J.G. Silva (Universidade de Coimbra, Portugal) |

| Session 6: Safety Chair: Bernd Eschermann, ABB Power Automation AG, Baden, Switzerland                                                                                                                         |

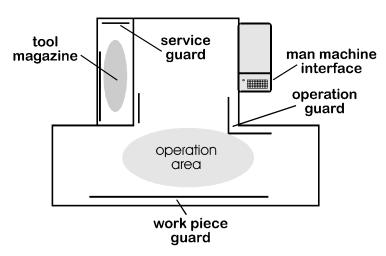

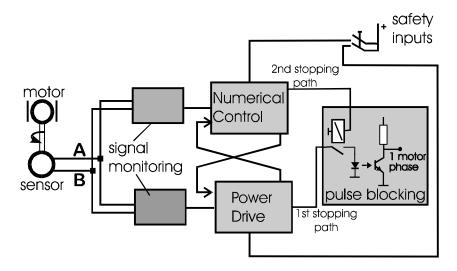

| Integrated Safety in Flexible Manufacturing Systems                                                                                                                                                            |

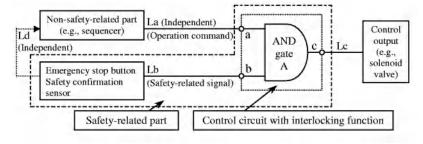

| A Method for Implementing a Safety Control System Based on Its Separation into Safety-Related and Non-Safety-Related Parts                                                                                     |

| Session 7: Hardware Testing Chair: Raimund Ubar, Tallin Technical University, Estonia                                                                                                                          |

| Design of Totally Self-Checking Code-Disjoint Synchronous Sequential Circuits . 251<br>J.W. Greblicki, S.J. Piestrak (Wrocław University of Technology, Poland)                                                |

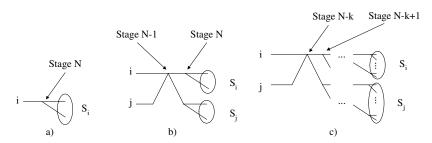

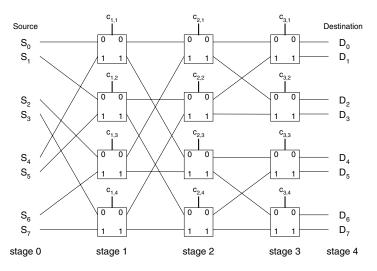

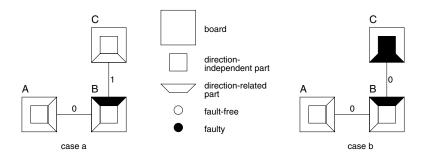

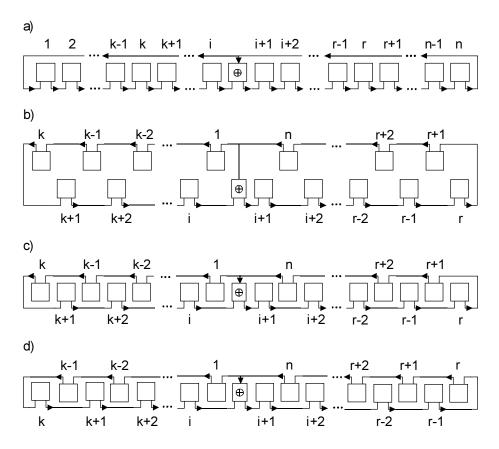

| Path Delay Fault Testing of a Class of Circuit-Switched Multistage Interconnection Networks                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M. Bellos (University of Patras, Greece), D. Nikolos (University of Patras, and Computer Technology Institute, Patras, Greece), H.T. Vergos (Computer Technology Institute, Patras, Greece)                                                                                                                             |

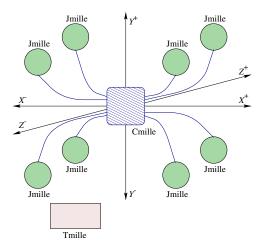

| Diagnostic Model and Diagnosis Algorithm of a SIMD Computer                                                                                                                                                                                                                                                             |

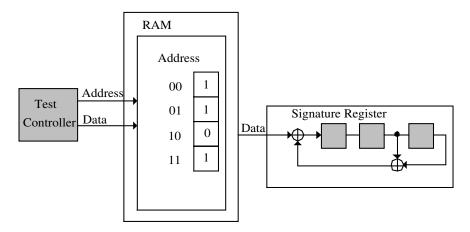

| Session 8: Built-In Self-Test  Chair: Bernd Straube, Fraunhofer Gesellschaft, Institute for Integrated Circuits,  Germany                                                                                                                                                                                               |

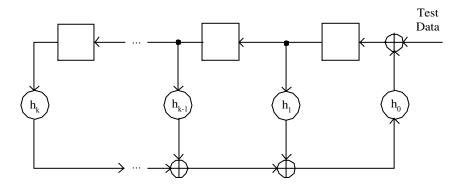

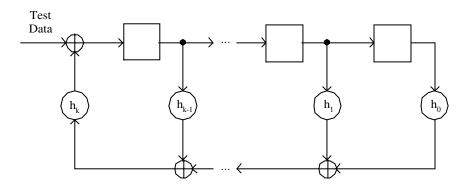

| Pseudorandom, Weighted Random and Pseudoexhaustive Test Patterns Generated in Universal Cellular Automata                                                                                                                                                                                                               |

| A New LFSR with D and T Flip-Flops as an Effective Test Pattern Generator for VLSI Circuits                                                                                                                                                                                                                             |

| Transparent Word-Oriented Memory BIST Based on Symmetric March Algorithms 339 V.N. Yarmolik (Belorussian State University, Minsk, Belarus, and Bialystok University of Technology, Poland), I.V. Bykov (Belorussian State University, Minsk, Belarus), S. Hellebrand, HJ. Wunderlich (University of Stuttgart, Germany) |

| Session 9: Networks and Distributed Systems Chair: Gilles Muller, INRIA/IRISA, Rennes, France                                                                                                                                                                                                                           |

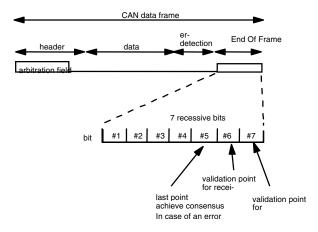

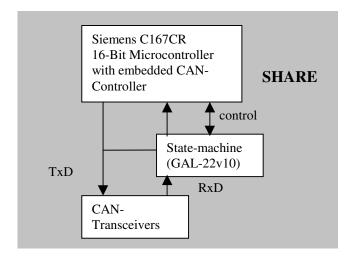

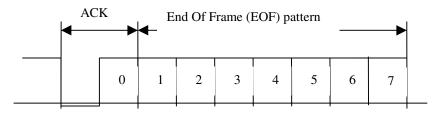

| Achieving Fault-Tolerant Ordered Broadcasts in CAN                                                                                                                                                                                                                                                                      |

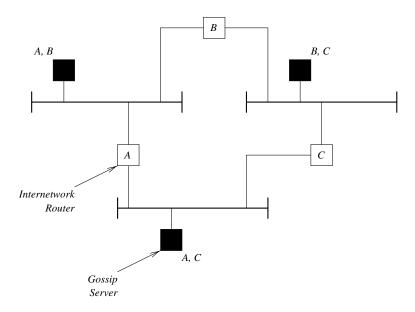

| Directional Gossip: Gossip in a Wide Area Network                                                                                                                                                                                                                                                                       |

| Efficient Reliable Real-Time Group Communication for Wireless Local Area Networks                                                                                                                                                                                                                                       |

| Session 10: Software Testing and Self-Checking Chair: Luca Simoncini, CNUCE/CNR, Pisa, Italy                                                                                                                                                                                                                            |

| A Case Study in Statistical Testing of Reusable Concurrent Objects                                                                                                                                                                                                                                                      |

#### XVIII

| Fault-Detection by Result-Checking for the Eigenproblem                                                                           | 419 |

|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| P. Prata (Universidade da Beira Interior, Covilhã, Portugal),                                                                     |     |

| J.G. Silva (Universidade de Coimbra, Portugal)                                                                                    |     |

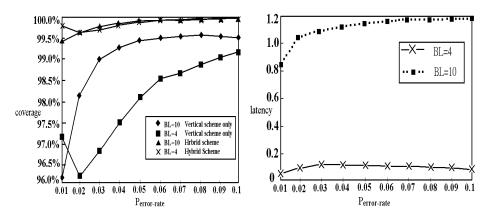

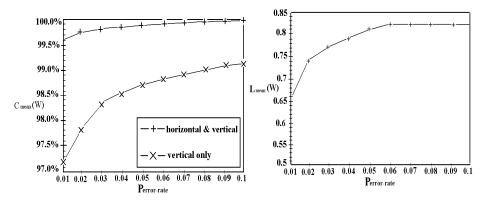

| Concurrent Detection of Processor Control Errors by Hybrid Signature Monitoring YY. Chen (Chung-Hua University, Hsin-Chu, Taiwan) | 437 |

| Author Index                                                                                                                      | 455 |

# **Reliable and Secure Operation of Smart Cards**

Horst H. Henn

Smart Card Solution Development, Dept. 3289

IBM Germany, Böblingen,

Schönaicher Str. 220

D-71032 Böblingen, Germany

hhenn@de.ibm.com

Smart cards are a key system component in distributed web based applications. Smart cards perform highly critical operations like electronic payment, digital signature and key management. Secure and dependable operation must be assured in normal and manipulated environment. Typical failure modes and attacks as well as protection schemes are described for smart card hardware and software. Certification methodology of smart card systems for state of the art systems like GELDKARTE and MONEO as well as requirements for ITSEC=6 security level are evaluated.

# Dependability Modelling and Sensitivity Analysis of Scheduled Maintenance Systems

Andrea Bondavalli<sup>1</sup>, Ivan Mura<sup>1</sup>, and Kishor S. Trivedi<sup>2</sup>

<sup>1</sup> CNUCE/CNR, Via Santa Maria 36, I-56126 Pisa, Italy {a.bondavalli, ivan.mura}@cnuce.cnr.it <sup>2</sup> CACC, Dept. of ECE, Duke University, Box 90291 NC 27708 Durham, USA kst@ee.duke.edu

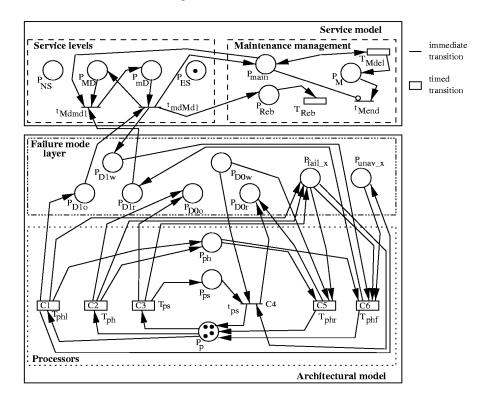

Abstract. In this paper we present a new modelling approach for dependability evaluation and sensitivity analysis of Scheduled Maintenance Systems, based on a Deterministic and Stochastic Petri Net approach. The DSPN approach offers significant advantages in terms of easiness and clearness of modelling with respect to the existing Markov chain based tools, drastically limiting the amount of user-assistance needed to define the model. At the same time, these improved modelling capabilities do not result in additional computational costs. Indeed, the evaluation of the DSPN model of SMS is supported by an efficient and fully automatable analytical solution technique for the time-dependent marking occupation probabilities. Moreover, the existence of such explicit analytical solution allows to obtain the sensitivity functions of the dependability measures with respect to the variation of the parameter values. These sensitivity functions can be conveniently employed to analytically evaluate the effects that parameter variations have on the measures of interest.

## 1 Systems with Multiple Phases and Multiple Missions

With the increasing complexity and automation encountered in systems of the nuclear, aerospace, transportation, electronic, and many other industrial fields, the deployment of processing systems in charge of performing a multiplicity of different control and computational activities is becoming common practice. Very often, the system and its external environment can be altered during the operation, in a way that the behaviour during a time interval can be completely different from that within other periods.

The operational scenario devised for the Scheduled Maintenance System (SMS) problem is a typical one in the context of the on-board aeroplane control systems. SMS are to be used during their life-time for multiple missions. The system is run for a finite number of missions, and then it has to pass a maintenance check. Such maintenance can be more or less extensive and accurate. Typically, it is the case that after a prefixed number of missions the system is completely checked, so that all its components are as good as new ones after that. Moreover, other kinds of maintenance actions are usually performed between two major checks. For instance, some highly critical components could be checked and possibly repaired after each mission, and

J. Hlavicka et al (Eds.): EDCC-3'99, LNCS 1667, pp. 7-23, 1999

some others could be replaced after some missions even if they are still working. Anyway, these partial checks are not able to guarantee the absence of faulty components in the system, and thus the dependability figures of the SMS inside a mission are affected by the past history of the SMS inside the previous missions. Within each mission, an SMS behaves as a phased mission system (PMS), that is it is has to carry out various operational phases, each of them possibly having specific dependability requirements and particular failure criteria. Specifically, the typical phases of an aeroplane mission include a take off, ascent, cruise, descent, approach and landing phases. Once again, since the same architectural components are to be used by the system, the behaviour of the SMS during a particular phase is affected by its past evolution while inside other phases of the same mission.

It is quite intuitive that an SMS can be reduced to a PMS, by simply disregarding the multiple missions, and considering all the phases to be executed as being part of a long mission. In this way, all the methods that have been proposed for the dependability analysis of PMS, also apply to SMS. Because of their deployment in critical applications, the dependability modelling and analysis of PMS has been considered a task of primary relevance, and many different approaches have appeared in the literature [4, 8, 13, 15, 17-19]. However, the modelling of complex systems always poses formidable problems, and PMS do not represent an exception to the rule. Moreover, the phased behaviour adds a further degree of complexity to the analysis of these systems. Modelling a PMS can be a complex task even inside one single phase; when a multiplicity of phases and the dependencies among them are to be taken into account, additional difficulties are encountered. The sole methodology specifically designed for the dependability modelling and evaluation of the SMS has been proposed by Somani et al., who implemented it within the EHARP tool [18] (an extension of the HARP tool). Some further extensions of EHARP for the SMS problem were introduced by Twigg et al. in [20]. The EHARP tool is based on a separate Markov chain modelling of the SMS inside the various phases, an approach that is able to effectively master the complexity and the computational cost of the analysis. However, as carefully explained in [15], this separate Markov based modelling approach requires a relevant amount of user-assistance to correctly model the dependencies among successive phases.

In this work, we show how the general methodology based on the Deterministic and Stochastic Petri Nets (DSPN) proposed in [15] for the modelling and evaluation of PMS can be applied to the specific case of the SMS problem. Thanks to the expressiveness of the DSPN, the modelling of systems showing a phased behaviour becomes quite intuitive and simple. The specific features of SMS are easily accommodated within our general modelling scheme, and the resulting model is defined in a very compact way, with a dramatic reduction in the number of the interactions with the user and the consequent reduction in possible errors. Indeed, the treatment of the dependencies among phases is moved from the low level of the Markov chains to the more abstract and easier to handle level of the DSPN. The evaluation procedure of the DSPN model of an SMS is supported by the existence of an efficient analytical solution method for the transient probabilities of the underlying marking process.

Moreover, we offer in this paper another relevant contribution to the study of systems with multiple phases, either PMS or SMS. The existence of analytical expressions for the time-dependent marking occupation probabilities of the DSPN models of this class of systems allows us to explicitly derive the sensitivity functions

of the dependability measures of interest, that is the analytical form of the derivatives of the measures with respect to the variations of a set of parameters. The steady-state sensitivity analysis of DSPN has been presented in [6], whereas the time-dependent sensitivity analysis of DSPN models is a task that has not been attacked yet, to the best of our knowledge. Such a transient sensitivity analysis can fruitfully complement the means available for the study of PMS and SMS, providing guidelines for the system optimisation, and in some cases avoiding or limiting the need of performing long batches of evaluations for a number of different values of the parameters [9].

The rest of this paper is organised as follows. Section 2 describes the most peculiar characteristics of SMS, and presents a simple case study that we will consider as a convenient application example throughout the paper. In Section 3 we introduce our DSPN approach and detail it by completely carrying out the modelling of the SMS taken as example. Then, the analytical solution of the DSPN models of SMS is briefly addressed in Section 4. In that same section, we also discuss on the opportunity and advantages offered by the sensitivity analyses to gain deeper insights into models and systems, and present the general guidelines for the derivation of the sensitivity functions for the measures of interest. Section 5 presents the results of a numerical evaluation conducted on the example of SMS, aiming at demonstrating the advantages of performing sensitivity analyses. Finally, Section 6 presents some concluding remarks.

#### 2 The SMS Problem

Consider a SMS that executes m missions, each mission being characterised by a specific number of phases of given durations. We denote with  $n_i$  the number of phases mission i is divided in, i=1,2,...,m. Moreover, denote with  $P_{i,j}$  the j-th phase to be performed during mission i,  $j=1,2,...,n_i$ , i=1,2,...,m. As long as we are interested in an exact analytical solution, phase duration is restrained to be deterministic. In fact, only approximate solution techniques have been proposed in the literature for the case of random phase durations. This assumption can be more or less restrictive, depending on the very nature of the events that lead to phase changes. Anyway, we assume that phase  $P_{i,j}$  has a constant duration  $\tau_{i,j}$ ,  $j=1,2,...,n_i$ , i=1,2,...,m.

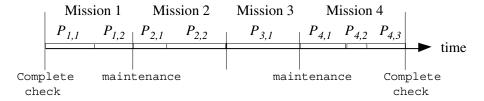

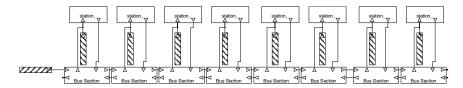

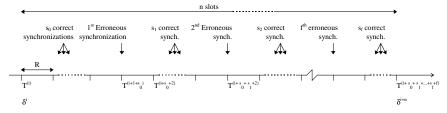

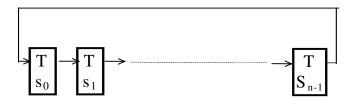

After completing the m missions, the SMS is subject to a complete maintenance check. Obviously, the study of system dependability can be limited to the period between two complete checks of the system, because after the check, the system is reset to its initial condition. Moreover, between these major checks, the system may be subject to less exhaustive and less expensive maintenance actions, which however affect the dependability figures of the system. Therefore, a proper modelling of the maintenance actions plays a relevant role for an accurate dependability evaluation. All the maintenance actions are considered instantaneous, because they are performed when the system is non operative. Therefore, they are also referred to as discrete repairs. The picture in Figure 1 shows an example of a possible maintenance schedule during the SMS life-time.

The proper scheduling of maintenance actions is a non trivial problem. From a dependability viewpoint, the best possible option is to completely check the SMS at

end of each mission. However, the cost of such simplistic solution is unacceptable because of the consequent under utilisation of the system. On the other hand, increasing the number of missions between two complete checks worsens the dependability figures of the SMS, with the risk of incurring in a catastrophic failure. The proper balance between system utilisation and dependability of operation can be formulated as an optimisation problem, for which dependability modelling provides a useful solution tool.

Fig. 1. Life-cycle of a SMS

To better explain our DSPN approach through an application case, we consider a simple example of SMS, inspired by the one that has been studied in [20]. Consider a system equipped with two components. Component A is a primary unit providing some functionality to the system, and component B acts as a backup unit for component A. The system is equipped with a switching logic, so that when A fails, the control of operation is immediately passed to B.

The system executes cyclically two different types of mission. Mission I encompasses a single phase  $P_{1,I}$  of fixed duration  $\tau_{1,I}$ , whereas mission 2 is a two phased mission, whose phases  $P_{2,I}$  and  $P_{2,2}$  have duration  $\tau_{2,I}$  and  $\tau_{2,2}$ , respectively. The time to failure of component A is exponentially distributed, with parameter  $\lambda_{I,A}$  during the missions of type I, and parameters  $\lambda_{2,A}$  during the type 2, respectively, whereas the time to failure of component B is constantly  $\lambda_B$ . The switching part is assumed to be fault-free. The system is assumed to be functional as long as either A or B are working.

The following scheduled maintenance actions are undertaken during system lifetime:

- The system is subject to a complete and exhaustive maintenance check each one hundred missions.

- Primary unit A is replaced at the end of each mission, if failed. After the replacement, A takes again the role of primary unit.

- Backup unit B is subject to a partial check at the end of each  $\alpha$  pairs of missions. So, after one hundred missions all the components are checked, and the system is restored to the initial condition. The Reliability of the system must be studied over the time interval between the beginning of the first mission and the end of the hundredth one. System failure is defined as the failure of A and B, and can be a catastrophic event that leads to a relevant economic loss. The occurrence probability of a system failure during the one hundred missions is denoted by F, and can be computed as I-R, where R is the Reliability of the system at the end of the one hundred missions.

Moreover, from a point of view of the system optimisation, we intend to determine whether it is economically convenient to increase the number  $\alpha$  of checks, or to increase the coverage c of the intermediate checks. Increasing the number of checks on the backup unit B has the effect of reducing the occurrence probability F. However, the check is a long operation, which requires the system to be not operative for a long period. For a global optimisation of the maintenance actions, the cost of such under utilisation of the system must be weighted with the potential cost paid in case of system failure. Suppose a cost  $\Phi$  is paid in case F occurs during the one hundred missions, and a cost  $\varphi$  is paid (say in terms of time) to perform the partial check of B each  $\alpha$  pairs of missions. The cost  $\varphi$  of the check and the overage c that it provides obviously depend from each other: the higher the target coverage, the more expensive the check required. We use the mathematical notation  $\varphi = \varphi(c)$  to denote such dependency. Then, to optimise the SMS with respect of the schedule of the maintenance, one should minimise the following overall expected cost function:

$$Cost = \boldsymbol{\Phi} \cdot Prob[F] + \varphi(c) \cdot \left\lfloor \frac{50}{\alpha} \right\rfloor = \boldsymbol{\Phi} \cdot (I - R) + \varphi(c) \cdot \left\lfloor \frac{50}{\alpha} \right\rfloor \tag{1}$$

We now briefly present the EHARP approach to the modelling and evaluation of SMS, by discussing its application to the example sketched above. EHARP is a tool especially designed for the Reliability analysis of SMS. The failure-repair model of the SMS is built as a continuous-time Markov chain, which may be different for each phase and each mission of the SMS. In the case of our example, there are two different Markov models, because the failure characteristics of the two SMS components differ during the missions of type 1 and 2.

The various Markov models are of course dependent from each other, in that the same components are to be used within various phases and missions. For instance, in our example if the primary A fails during the first phase of a type 2 mission, this will affect the operation in the successive second phase, and thus the memory of the past evolution is to be kept from one phase to the other. Similarly, if the backup component B fails and it is not repaired by a maintenance check at the end of the mission, then such a latent failure will affect the dependability of the subsequent missions. To model these dependencies, a set of phase-to-phase mapping functions must be specified. Starting from the final state occupation probability vector of a phase, these functions assign the initial state occupation probabilities over the states of the Markov chain of the next phase. Similarly, a set of mission-to-mission mapping functions need to be specified, to map the state occupation probabilities at the end of a mission to the start of the next one. In the EHARP environment, these functions are restricted to be linear functions, so that they can be represented as matrices.

It is worthwhile observing that the specification of the mapping matrices requires a considerable amount of user interaction. Though not conceptually complicated, the manual specification of these matrices may become a long and tedious job, and more importantly it certainly becomes an error-prone task for large Markov models.

A non trivial point the author of [20] also consider, is the specification of the maintenance actions. The definition language of the EHARP tool allows the introduction of maintenance directives such as the following one:

Repair

$$X$$

at interval  $n$  if  $B = True$

whose meaning is to declare that component X is to be repaired at the end of the n-th mission, provided that predicate B holds of the state of the system at that time. All

the repair directives have to be manually translated into mapping matrices, and are included in the same mapping matrices used to represent the dependence among successive phases and successive missions. Indeed, the instantaneous repair caused by maintenance actions is easily incorporated into the structural changes the SMS usually experiences as a result of the phase-dependent characteristics.

However, this treatment of the maintenance actions further increases the amount of user-assistance needed to define the models. As the authors of [20] themselves affirm:

[...] manual specification of the state to state mapping is tedious except for very small systems. Much energy has been devoted to compact specification methods for state dependent failure mechanisms, but the authors do not know a compact specification method for discrete repairs.

As we shall see in the following, the DSPN approach to the modelling of SMS overcomes this limitations of the methods in the literature, completely avoiding the need of any user-assistance in the treatment of the phase dependencies and in the specification of the maintenance actions.

#### 3 The SMS Problem Viewed as a PMS

The methodology we apply in this section to the modelling of our example of SMS is directly derived from the one we devised for PMS in [15]. The additional specific features of SMS are immediately included in our general modelling scheme, and exploited to achieve a compact representation of the multiple missions performed during the life-cycle. We show the potentialities of the DSPN approach and highlight the advantages it offers with respect to the classical modelling with Markov chains.

The modelling of the SMS is based on a single DSPN modelling approach, though the model is logically split in the following three parts:

- the Mission Net submodel (MN), which represents the consecutive execution of the various missions between two complete checks of the SMS.

- the Phase Net submodel (PhN), which models the alternation of phases during the execution of the various missions;

- the System Net submodel (SN), which represents the failure-repair model of the system components inside the various phases;

It is worth noting that the different submodels logically reflect the inherent hierarchy of the problem, that is the one existing among life-cycle, missions, and phases of a SMS. Each of the submodels may be dependent from the other ones. So, the evolution of the SN submodel is made dependent from the marking of the PhN and MN to model the mission and phase particularities of the failure/repair characteristics of the system. Similarly, the PhN evolution may be governed by the status of the MN submodel, and vice versa.

These dependencies are conveniently modelled through the use of marking-dependent guards on transitions, timed transition priorities, halting conditions, reward rates, etc. These expressive modelling features are already available under the Stochastic Reward Nets and Stochastic Activity Networks modelling paradigms and their associated automated tools SPNP [7] and UltraSAN [16], and are being more and more included in other automated tools for the evaluation of system dependability, such as DSPNexpress [11, 12], PANDA [1], and SURF-2 [2].

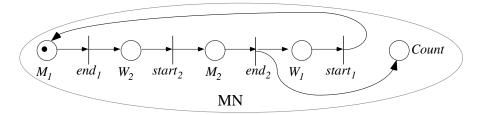

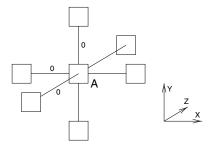

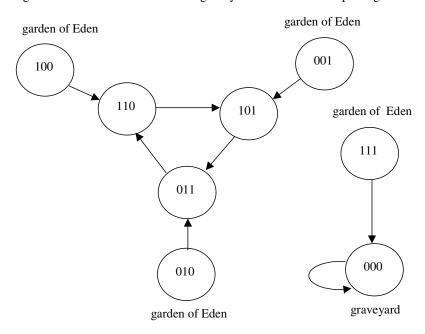

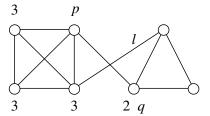

We now apply our modelling methodology to the example of PMS defined in the last section. The topmost level submodel MN shown in Figure 2 includes a single

token circulating in it, four places  $M_1$ ,  $M_2$ ,  $W_1$ , and  $W_2$ , and four immediate transitions  $end_1$ ,  $end_2$ ,  $start_1$ , and  $start_2$ . A token in place  $M_i$  models the execution of a type i mission, and the firing of a transition  $end_i$  represents its completion, i=1,2. Place  $W_i$  and transition  $start_i$ , i=1,2, are employed to model the synchronisation between the MN and the PhN submodels at the end of each mission. The place Count has been included to provide a compact representation of the SMS, by exploiting its cyclic behaviour. The number of tokens in place Count keeps track of the number of missions performed by the SMS. The MN model is not limited to have a particular structure. A simple chain linking all the possible missions can be used if the SMS does not exhibits any regular pattern in the execution of the missions. More compact structures as the one shown in Figure 2 can be defined if some missions are periodically performed.

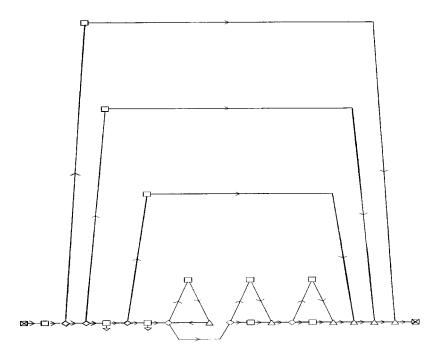

Fig. 2. Topmost MN submodel of a SMS

Since a mission starts only after the preceding one has completed, the definition of the MN model is to be completed by a set of enabling conditions, also called guards, that control the firing of the immediate transition  $end_i$  and  $start_i$ , i=1,2. These enabling conditions are defined in terms of the marking of the PhN submodel shown in Figure 3, and are listed in Table 1. Notice that these marking dependent guards are not intended to substitute the classic enabling rules of Petri net model transitions, rather they represent additional constraints that must be fulfilled for a transition to be eligible for firing.

| Transition                              | Enabling condition |  |

|-----------------------------------------|--------------------|--|

| end <sub>1</sub> , end <sub>2</sub>     | m(Stop) = 1        |  |

| start <sub>1</sub> , start <sub>2</sub> | $m(P_1) = 1$       |  |

**Table 1.** MN marking dependent enabling conditions

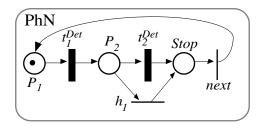

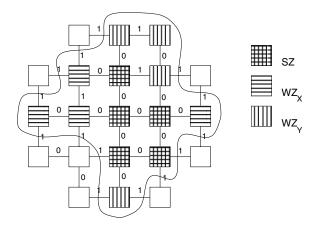

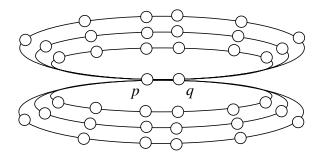

The PhN submodel concisely represents in a single net the two possible types of mission executed by the SMS. To explain the evolution of the PhN model, suppose first that the SMS solely executes mission of type 2, which consist of two consecutive phases. The two deterministic transitions  $t_1^{Det}$  and  $t_2^{Det}$  model the time needed for the SMS to perform the two phases of a type 2 mission. A single token circulates in the PhN. A token in place  $P_1$  enables transition  $t_1^{Det}$ , modelling the execution of the first phase of the mission. Similarly, a token in the place  $P_2$ , enables

transition  $t_2^{Det}$ , modelling the execution of the second phase. To represent on this same model the execution of the single phased type I missions, too, we introduce the immediate transition  $h_I$ , which directly moves the token to the place Stop. Thus, a single phase mission is modelled by skipping the deterministic transition  $t_2^{Det}$ .

Fig. 3. PhN submodel of a SMS

This dynamic selection of the path to be followed is modelled by the enabling conditions shown in Table 2, which rule the firing of the PhN transitions depending on the marking of the MN submodel. As soon as it reaches place Stop, the token is moved back to place  $P_I$  by the instantaneous transition next, which models the beginning of the next mission. It is worthwhile observing that this compact modelling of the set of possible missions becomes particularly convenient when several missions are repeated between the complete maintenance checks.

| Transition  | Firing time                                                      | Enabling condition    |

|-------------|------------------------------------------------------------------|-----------------------|

| $t_1^{Det}$ | $\tau_{1,1}$ , if $m(M_1) = 1$<br>$\tau_{2,1}$ , if $m(M_2) = 1$ | TRUE                  |

|             | $\tau_{2,1}$ , if $m(M_2) = 1$                                   |                       |

| $t_2^{Det}$ | $	au_{2,2}$                                                      | $m(M_2) = 1$          |

| $h_1$       | instantaneous                                                    | $m(M_1) = 1$          |

| next        | instantaneous                                                    | $m(W_1) + m(W_2) = 1$ |

**Table 2.** PhN marking dependent parameters

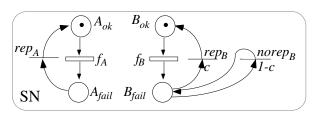

Following the same approach as in the case of the PhN, we define a single SN submodel that actually specialises into different models, depending on the marking of the SMS. The SN submodel for our example of SMS is shown in Figure 4.

Fig. 4. System Net submodel

A token in place  $A_{ok}$  or  $A_{fail}$  models the fact that component A is correctly working or failed, respectively, and similarly for component B. The failure process of components A and B is modelled by the exponential transition  $f_A$  and  $f_B = \lambda_B$ , respectively. Since the failure intensity is different depending on the type of mission, the firing time of  $f_A$  is dependent on the marking of the MN submodel, as specified in Table 3.

Table 3. Marking dependent firing rates of the SN submodel

| Transition | Firing rate                                                       |

|------------|-------------------------------------------------------------------|

| $f_A$      | $\lambda_{1,A}$ if $m(M_1) = 1$ , $\lambda_{2,A}$ if $m(M_2) = 1$ |

The discrete repairs that take place as a consequence of the maintenance actions are modelled by introducing the immediate transitions  $rep_A$ ,  $rep_B$ , and  $norep_B$ . These immediate transitions are enabled at the end of those missions for which a maintenance action has been scheduled. To ensure a proper sequence of firing of the immediate transitions in the model, the discrete repair transition are assigned a priority higher than that of transition next in the PhN submodel. The two conflicting transitions  $rep_B$  and  $norep_B$  fire with probability c and l-c, modelling the coverage of the intermediate maintenance check on component B. To properly model the execution of the scheduled maintenance action, the enabling conditions shown in Table 4 are added to the immediate transitions  $rep_A$ ,  $rep_B$ , and  $norep_B$ .

**Table 4.** SN marking dependent enabling conditions

| Transition | Enabling condition                                                               |

|------------|----------------------------------------------------------------------------------|

| $rep_A$    | m(Stop) = 1                                                                      |

| $rep_B$    | $m(Stop) = 1 \& m(Count) = \alpha \cdot i, i = 1, 2,, \lfloor 50/\alpha \rfloor$ |

| $norep_B$  | $m(Stop) = 1 \& m(Count) = \alpha \cdot i, i = 1, 2,, \lfloor 50/\alpha \rfloor$ |

Similarly, we can model maintenance directives requiring the repair of components between two phases of a mission, or whatever change of configuration that takes place at the end of a phase. Moreover, as we have detailed in [15], this same mechanism of conditioning the evolution of a part of the model through a set of marking dependent parameters can be used to model more general scenarios of multi phased missions. In particular, by conditioning the MN and PhN submodels to the marking of the SN one it is possible to represent more dynamic and flexible SMS, where the next phase or mission to be performed can be chosen depending on the state of the system.

It is important to spend a few words in pointing out the advantages of the DSPN modelling of SMS. First of all, the high-level approach turns out in a overall SMS model that is concise, easy to understand and to modify. Moreover, the whole modelling procedure limits the possibility of introducing errors inside the models. Various structural properties of the separate Petri net submodels can be checked to increase the confidence that can be put in the modelling itself. Further, the links among the various submodels are expressed through predicates of the marking, in a clear and unam-

biguous way. The tedious process of manual description of the mapping and the translation of maintenance directives into matrices, which is necessary with the EHARP approach, is completely eliminated. Indeed, the mapping between successive phases and missions and the maintenance actions are completely specified at the level of the DSPN modelling. The mapping at the level of the underlying Markov chains is automatically obtained from the analysis of the reachability graph of the DSPN model, thus dramatically reducing the amount of user-assistance needed to define the SMS models. Finally, as we shall see in the following, these modelling capabilities are also sustained by a very efficient analytical solution technique.

#### 4 Analytical Solution and Sensitivity Analysis

As it has been proved in [5], a DSPN model can be analytically solved in terms of the time-dependent marking occupation probabilities by applying the results of the MRGP theory, provided that at most one deterministic transition is enabled in each of the possible markings of the net. This condition is obviously satisfied for the DSPN model of a SMS, because the only deterministic transitions of the model are those in the PhN, and they get enabled sequentially, one at the time. Moreover, due to the special structure of the system, the computationally efficient method proposed in [15] applies for the solution of the models. In the following, we briefly recall that method, for deriving first the exact analytical expression for the transient marking occupation probabilities, and second the sensitivity of the dependability measures with respect to the parameter variations.

#### 4.1 Reliability at Mission Completion Time

To avoid a cumbersome notation, during this solution step we flatten the multiple mission structure of the SMS, reducing it to a PMS structure. Thus, we renumber the phases along the various missions, so that we consider a single long mission, during which all the  $N = \sum_{i=1}^m n_i$  phases of the SMS are sequentially executed. Let  $\tau_i$  denote the time the SMS spends in phase i of the mission, and  $Q_i$  denote the transition rate matrix that describes the evolution of the SN submodel while the SMS executes phase i, i = 1, 2, ..., N. During the execution of a phase i, the evolution of the marking process underlying the DSPN model follows that of a simple continuous-time Markov chain, and is thus described by the exponential of the matrix  $Q_i$ .

According to the results presented in [15], the vector  $\pi(t)$  of the time-dependent marking occupation probabilities of the DSPN model can be explicitly computed for any time  $t \ge 0$ . From vector  $\pi(t)$  all the dependability measures of interest can be obtained. For instance, we can obtain the Reliability R of the SMS at the end of the last phase N, which is given by the following expression:

$$R = \pi_0 \cdot \left( \prod_{h=1}^N e^{Q_h \tau_h} \Delta_h \right) \cdot \beta \tag{2}$$

where  $\pi_0$  is the vector of initial probability assignment,  $\Delta_h$  is the branching-probability matrices which account for the branching probabilities as the deterministic transition i fires i=1,2,...,N, and  $\beta$  is a vector that selects the successful states at the end of the hundredth mission. It is worthwhile observing that evaluating the preceding formula to obtain the transient state probability matrix only requires us to derive matrices  $e^{Q_h \tau_h}$ , and  $\Delta_h$ , h=1,2,...,N. All the required matrices can be derived from the analysis of the DSPN reachability graph. The solution of the single DSPN model is reduced to the cheaper problem of deriving the transient probability matrices of a set of homogeneous, time-continuous Markov chains whose state spaces are proper subsets of the whole state space of the marking process.

#### 4.2 Sensitivity Analysis

The existence of an analytic expression for the marking dependent occupation probabilities allows to evaluate the derivatives of the dependability measures of interest with respect to the variations of some parameters, the so-called sensitivity functions [9]. These functions can be conveniently employed to perform an analytical study of the effects that the parameter variations have on the dependability. Indeed, the absolute value of the derivative indicates the magnitude of the variations of the measure for a small perturbations of the parameter, and its sign reveals whether an increase of the parameter value causes a corresponding increase or instead a decrease of the measure.

Obviously, whenever the dependence of the measure of interest from the parameters only involves simple functions that can be computed at a limited computational cost, the sensitivity analysis can be conveniently conducted through multiple evaluations, to plot the dependability measures for the whole range of parameter values. However, when more parameters can be varied simultaneously, this approach tends to become expensive in terms of the number of evaluations. In this scenario, the study of the sensitivity functions represents a suitable strategy to point out which parameters of the system most significantly impact on the measures of interest. Indeed, by comparing the partial derivatives with respect to the varying parameters it is possible to identify those to which the measures are sensitive the most.

Conversely, when the dependability measure object of the evaluation is a complex function, performing multiple evaluations can easily become an expensive task. For instance, consider the formula for the SMS Reliability given by Equation (2), and suppose we want to estimate the effect that varying the failure rate  $\lambda_A$  has on the measure. Then, since the parameter  $\lambda_A$  appears inside the transition rate matrices  $Q_i$ , for each value of  $\lambda_A$  we need to evaluate a set of matrix exponentials. In this case, the sensitivity function of the Reliability with respect to parameter  $\lambda_A$  can fruitfully complement the means available for the study of a SMS, in some cases avoiding or limiting the need of performing long batches of evaluations for a number of different values of the parameters.

We now obtain the sensitivity function of the Reliability R given by Equation (2), with respect to an independent parameter  $\theta$ , that is we consider  $R = R(\theta)$ . The analytical derivation of this derivative is just an example of the sensitivity studies that can be performed once the analytical expression for the dependability measures are available. The initial probability vector, the duration of phases, the firing rates of ex-

ponential transitions, as well as the probability mass functions ruling the firing of immediate transitions may be dependent on parameter  $\theta$ . Let us denote with  $\rho(\theta)$  the sensitivity function, defined as the derivative of  $R(\theta)$  with respect to  $\theta$ :

$$r(q) = \frac{\partial}{\partial q} R(q) = \left(\frac{\partial}{\partial q} p_0\right) \prod_{h=1}^{N} e^{Q_h t_h} D_h \cdot b + \pi_0 \cdot \frac{\partial}{\partial q} \left(\prod_{h=1}^{N} e^{Q_h t_h} D_h\right) \cdot b \tag{3}$$

The derivative of the product that appears in the last term of Equation (3) is obtained as follows:

$$\frac{\partial}{\partial \theta} \prod_{h=1}^{N} e^{Q_h \tau_h} \Delta_h = \sum_{k=1}^{N} \left[ \left( \prod_{h=1}^{k-1} e^{Q_h \tau_h} \Delta_h \right) \frac{\partial}{\partial \theta} e^{Q_k \tau_k} \Delta_k \left( \prod_{h=k+1}^{N} e^{Q_h \tau_h} \Delta_h \right) \right] \tag{4}$$

Last, the derivative of  $e^{Q_k \tau_k} \Delta_k$  can be obtained as follows:

$$\frac{\partial}{\partial \theta} e^{Q_k \tau_k} \Delta_k = \frac{\partial}{\partial \theta} \left( e^{Q_k \tau_k} \right) \Delta_k + e^{Q_k \tau_k} \frac{\partial}{\partial \theta} \Delta_k \tag{5}$$

By combining the intermediate results given by Equation (3), (4), and (5), we obtain the most general formula for the sensitivity function  $s(\theta)$ , for it takes into account the dependence from  $\theta$  of any other parameter of the DSPN model. It is worthwhile observing that, with respect to the evaluation of the Reliability R, the estimation of the sensitivity function only requires an additional small computation effort. Indeed, mostly the same matrices are required, according to Equations (2) and (3), (4), and (5). The only non trivial computation is that of the derivative of the matrix exponential, for which efficient algorithms have been defined [3, 10, 14]. Thus, once the value of the Reliability  $R(\theta)$  has been derived, its derivative  $\rho(\theta)$  can be evaluated too with a limited additional effort for a given value of  $\theta$ . The pointwise derivatives of the measure can be employed to increase the accuracy of the approximations of the measure over continuous intervals, through an interpolation approximation. Thus, the number of points at which the measure is plotted can be drastically reduced still achieving a good level of accuracy.

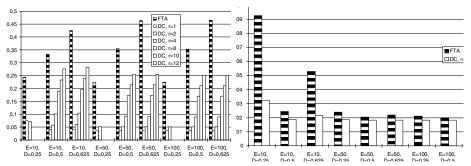

#### 5 Numerical Evaluation

In this section we present the results of a numerical evaluation of the dependability figures for the example of SMS we modelled above. In a first evaluation session we estimate R, the Reliability of the SMS at the mission completion time, with varying the values of some parameters, and complement the analysis by exploiting the information provided by the sensitivity functions. Then, mainly dealing with the sensitivity functions, we study in detail the cost function defined by Equation (1), to provide some hints for possible system optimisation.

The general analytical expression for Reliability R, given by Equation (2), can be rewritten according to the particular structure of our example of SMS. Since the firing rates of transitions  $f_A$  and  $f_B$  have different values depending on the type of mis-

sion, there are two distinct transition rate matrices, which we denote with  $Q_1$  and  $Q_2$ . Similarly, there are two types of maintenance checks, that is the one performed at the end of each mission, which solely involves component A, and that performed each  $\alpha$  pairs of missions, which affects both A and B. These two types of check are translated into two distinct branching probability matrices, denoted by  $\Delta_1$  and  $\Delta_2$ , respectively. As an instance, the following equation shows the formula of R for  $\alpha = 2$ :

$$R = \pi_0 \cdot (X \cdot Y \cdot X \cdot Z)^{25} \cdot \beta \tag{6}$$

where  $X = e^{Q_1 \tau_{I,1}} \Delta_I$   $Y = e^{Q_2(\tau_{2,1} + \tau_{2,2})} \Delta_I$ , and  $Z = e^{Q_2(\tau_{2,1} + \tau_{2,2})} \Delta_2$ . For this same value of  $\alpha = 2$ , we also show the sensitivity function of R with respect to the failure rate of the backup unit  $\lambda_B$ , denoted by  $\rho(\lambda_B)$ . According to the equations derived in the previous section, the sensitivity function  $\rho(\lambda_B)$  takes the following form:

$$\rho(\lambda_B) = \pi_0 \cdot \left[ \sum_{h=1}^{25} (X \cdot Y \cdot X \cdot Z)^{h-1} \cdot \left( \frac{\partial}{\partial \lambda_B} (X \cdot Y \cdot X \cdot Z) \right) \cdot (X \cdot Y \cdot X \cdot Z)^{25-h} \right] \cdot \beta \quad (7)$$

The derivative of matrix XYXZ is obtained according to Equation (5). It is worthwhile observing that the matrix powers computed during the evaluation of the Reliability for a given value of  $\lambda_B$  according to Equation (6) can be conveniently reused when evaluating the sensitivity function  $\rho(\lambda_B)$  in Equation (7), thus reducing the required computational cost.

We assume that at the beginning of operation both component A and B are perfectly working, and therefore the initial probability vector  $\pi_0$  is the one that assigns probability I to the marking in which both A and B are correctly working. Vector  $\beta$  selects those marking that represents a proper system state, that is all the markings except the one in which both A and B have failed. The fixed value parameters, that is the phase duration and the failure process of the primary unit A are given in Table 5. Hour (h) is the unit in which all time-related measures are expressed.

**Table 5.** Fixed value parameters of the SMS model

| Duration of the phases                                    | Failure rates of components                          |

|-----------------------------------------------------------|------------------------------------------------------|

| $\tau_{1,1} = 15h, \ \tau_{2,1} = 5h, \ \tau_{2,2} = 10h$ | $\lambda_{1,A} = 0.001/h, \ \lambda_{2,A} = 0.002/h$ |

The parameters related to the backup unit B, that is its failure intensity during the various missions, the coverage and the frequency of the check, are variable within the ranges specified by Table 6.

**Table 6.** Parameter values for component B

| Failure rate                                            | Check coverage      | Frequency of the check |

|---------------------------------------------------------|---------------------|------------------------|

| $\lambda_B \in [10^{-1}\lambda_{I,A}, 10\lambda_{I,A}]$ | $c \in [0.6, 0.99]$ | $\alpha = 1, 2, 5$     |

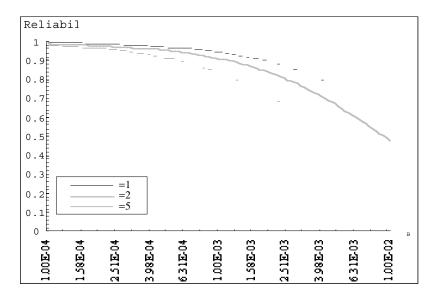

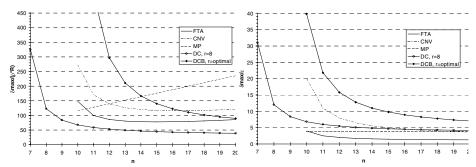

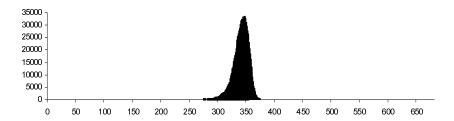

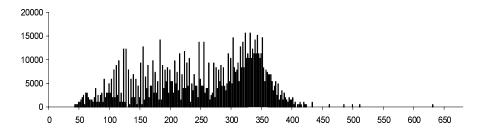

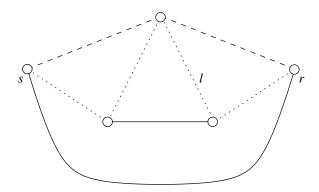

We first evaluate the Reliability R of the SMS with varying the failure rate of the backup unit  $\lambda_B$  within the considered range of values, for the various possible values of the period length  $\alpha$  between two intermediate maintenance checks, and a fixed value of the coverage c=0.95. The curves shown in Figure 5 help in clarifying the effect that the choice of a particular frequency has on the Reliability of the system.

Fig. 5. Reliability of the SMS for different settings of parameters

From the results shown in Figure 5, it is possible to identify a range of values of the failure rate  $\lambda_B$ , specifically the values on the left side of the plots, for which changing the period  $\alpha$  does not impact significantly on the final measure, whereas relevant changes in the SMS Reliability results can be observed for higher values of  $\lambda_B$ . As it would be expected, if reliable components are employed, the frequency of the check does not necessarily need to be particularly high to achieve satisfactory results.

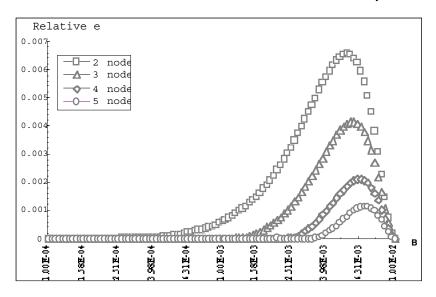

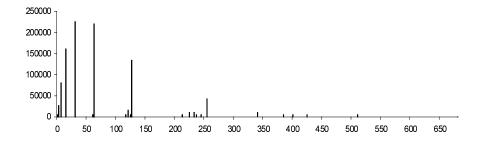

We now approximate the results obtained for the Reliability of the SMS by using the interpolation technique and compare the quality of the approximate results with respect to the amount of information that is needed to compute them. Letting  $\alpha=2$ , we interpolate the Reliability by considering an increasing number of interpolation points (the so-called interpolation nodes) to obtain more and more accurate approximation of the original Reliability figures. We consider four different approximate Reliability curves, obtained by interpolating the function and its derivative in two, three, four, and five nodes. The relative error introduced by the various interpolations over the whole interval of values considered for  $\lambda_B$  is shown in Figure 6. As it can be observed from the comparison in Figure 6, with five interpolation nodes we obtain a very tight approximation of the original curve, which was evaluated at one hundred points to produce the corresponding curve shown in Figure 5.

Fig. 6. Accuracy of Reliability approximation

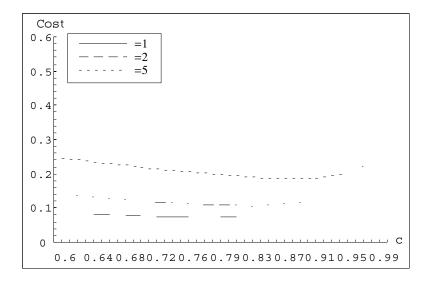

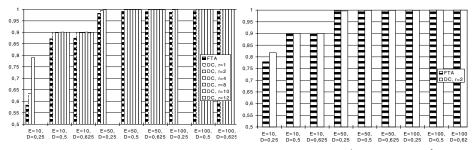

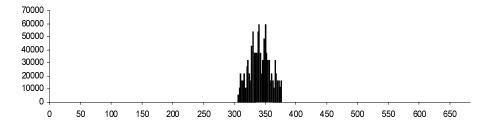

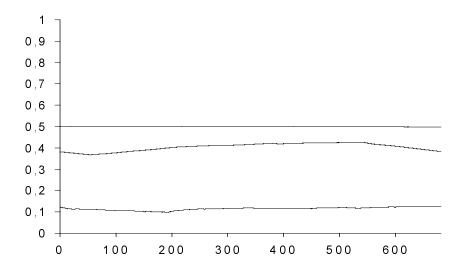

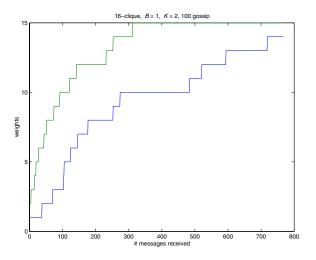

We now conduct a different set of numerical evaluations to study the cost function defined by Equation (1) with varying the coverage c of the check on the backup unit B, for a fixed value  $\lambda_B = \lambda_{I,A}$  of component B failure rate.

Fig. 7. Expected cost as a function of the intermediate check coverage

We assume the cost  $\Phi$  of the system failure as being unitary, and proportionally define the cost function  $\varphi(c) = k_I \cdot e^{k_2 c}$  in a way that a check providing coverage 0.6

requires a cost of  $10^{-6} \, \Phi$ , whereas a check with coverage 0.99 costs  $10^{-2} \, \Phi$ . Notice that these specific values are only chosen as an example to have the possibility of graphically interpreting the trends of the cost function, and do not have any pretension to reflect actual maintenance costs. We plot in Figure 7 the cost function for the different values of  $\alpha$ , and find the corresponding values of c that minimise the SMS expected costs. Moreover, from this graphical comparison, it is possible to identify, for any given value of c, the optimal schedule of the maintenance with respect to the cost function, that is the period  $\alpha$  that results in the minimum expected cost. For instance, for a coverage value of c = 0.95, the optimal period is  $\alpha = 2$ ,  $\alpha = 5$  provides a slightly worse cost, whereas  $\alpha = 1$  is significantly more expensive.

#### 6 Conclusions

In this paper we have introduced a new modelling approach for dependability evaluation and sensitivity analysis of Scheduled Maintenance Systems. The proposed methodology exploits the high level representative features of Deterministic and Stochastic Petri net models, to provide an intuitive and simple modelling strategy. Compared to the other approaches existing in the literature, which are mainly based on Markov chain modelling tools, the DSPN approach offers significant advantages, drastically limiting the amount of user-assistance needed to define the model of a SMS. Moreover, the DSPN model of a SMS can be analytically solved in terms of the time-dependent marking occupation probabilities for the purposes of dependability evaluation. The solution technique is very efficient in terms of computational cost, requires only standard numerical algorithms, and can be easily automated.

Furthermore, owing to the existence of the explicit analytical solution for the transient marking occupation probabilities, we have obtained the sensitivity functions of the dependability measures with respect to the variation of the parameter values. These sensitivity functions can be conveniently employed to analytically evaluate the effects that parameter variations have on the measures of interest.

To better show the advantages of our approach, we have applied our modelling methodology to an example of SMS that has been inspired by a case study encountered in the literature. We have completely carried out the modelling, derived the sensitivity function of the Reliability, and performed a set of numerical evaluations with the aim of finding the most appropriate schedule of maintenance for the example of SMS. By exploiting the additional information provided by the sensitivity functions, we have obtained very accurate approximations of the dependability measures through an interpolation approach, achieving a significant reduction of the evaluation computational costs.

#### References

- 1. S. Allmaier and S. Dalibor, "PANDA Petri net analysis and design assistant," in Proc. Performance TOOLS'97, Saint Malo, France, 1997.

- C. Beounes, M. Aguera, J. Arlat, C. Bourdeau, J.-E. Doucet, K. Kanoun, J.-C. Laprie, S. Metge, J. Moreira de Souza, D. Powell and P. Spiesser, "SURF-2: a program for dependability evaluation of complex hardware and software systems," in Proc. IEEE

- FTCS'23, Fault-Tolerant Computing Symposium, Toulouse, France, 1993, pp. 668-673.

- J. T. Blake, A. Reibman and K. S. Trivedi, "Sensitivity analysis of reliability and performability measures for multiprocessor systems," Duke University, Durham NC, USA 1987.

- 4. A. Bondavalli, I. Mura and M. Nelli, "Analytical Modelling and Evaluation of Phased-Mission Systems for Space Applications," in Proc. IEEE High Assurance System Engineering Workshop (HASE'97), Bethesda Maryland, USA, 1997, pp. 85 91.

- 5. H. Choi, V.G. Kulkarni and K.S. Trivedi, "Transient analysis of deterministic and stochastic Petri nets.," in Proc. 14th International Conference on Application and Theory of Petri Nets, Chicago Illinois, USA, 1993, pp. 166-185.

- 6. H. Choi, V. Mainkar and K. S. Trivedi, "Sensitivity analysis of deterministic and stochastic petri nets," in Proc. MASCOTS'93, 1993, pp. 271-276.

- G. Ciardo, J. Muppala and K.S. Trivedi, "SPNP: stochastic petri net package.," in Proc. International Conference on Petri Nets and Performance Models, Kyoto, Japan, 1989.

- 8. J. B. Dugan, "Automated Analysis of Phased-Mission Reliability," IEEE Transaction on Reliability, Vol. 40, pp. 45-52, 1991.

- 9. P. M. Frank, "Introduction to System Sensitivity Theory," New York, Academic Press, 1978.

- P. Heidelberger and A. Goyal, "Sensitivity analysis of continuous time Markov chains using uniformization," in Proc. 2-nd International Workshop on Applied Mathematics and Performance/Reliability models of Computer/Communication systems, Rome, Italy, 1987.

- 11. C. Lindemann, "Performance modeling using DSPNexpress," in Proc. Tool Descriptions of PNPM'97, Saint-Malo, France, 1997.

- C. Lindemann, "Performance modeling using deterministic and stochastic petri nets," John Wiley & Sons, 1998.

- 13. J.F. Meyer, D.G. Furchgott and L.T. Wu, "Performability Evaluation of the SIFT Computer," in Proc. IEEE FTCS'79 Fault-Tolerant Computing Symposium, June 20-22, Madison, Wisconsin, USA, 1979, pp. 43-50.

- 14. J. K. Muppala and K. S. Trivedi, "GSPN models: sensitivity analysis and applications," in Proc. 28-th ACM Southeast Region Conference, 1990.

- 15. I. Mura, A. Bondavalli, X. Zang and K. S. Trivedi, "Dependability Modeling and Evaluation of Phased Mission Systems: a DSPN Approach," in Proc. DCCA-99, San Jose, CA, USA, 1999.

- 16. W. H. Sanders, W. D. Obal II, M. A. Qureshi and F. K. Widjanarko, "The *UltraSAN* modeling environment," Performance Evaluation, Vol. 21, pp. 1995.

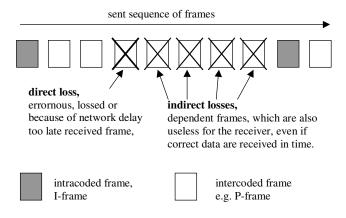

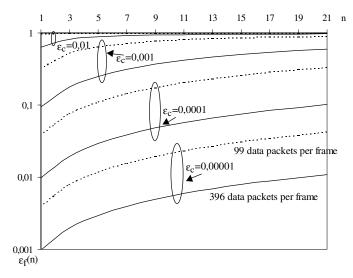

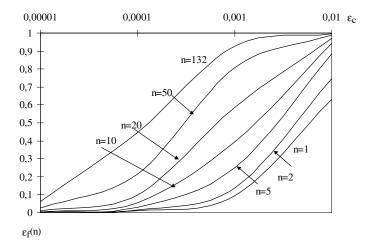

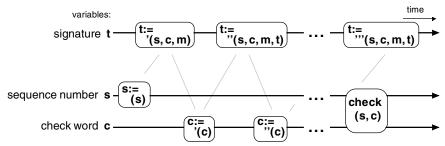

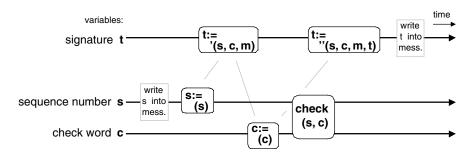

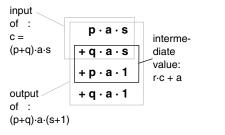

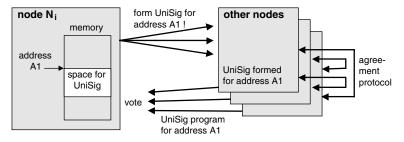

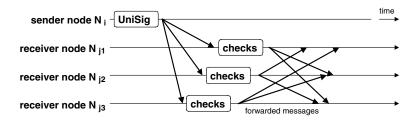

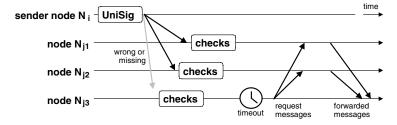

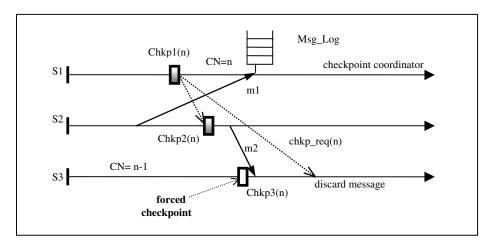

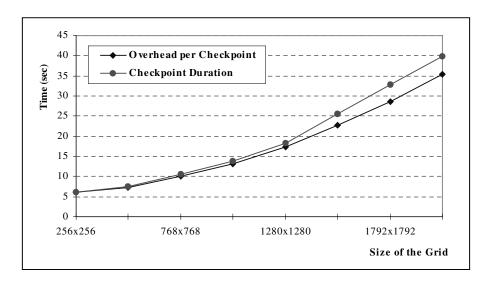

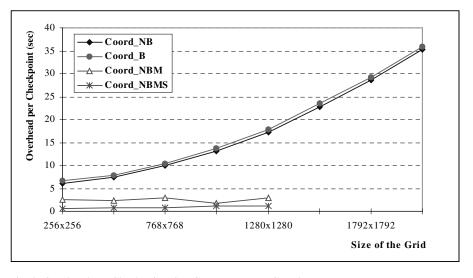

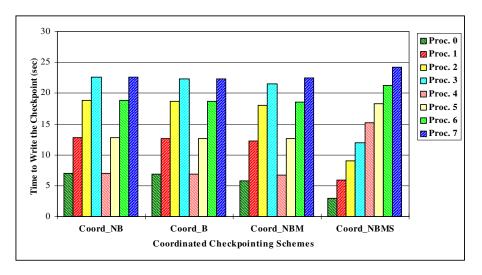

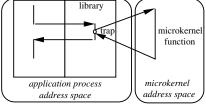

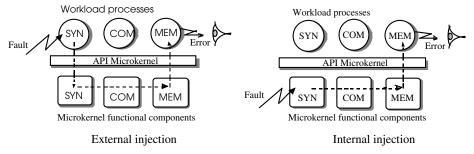

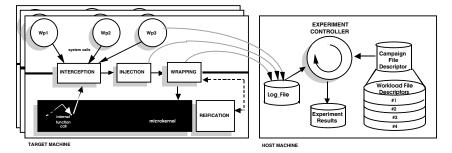

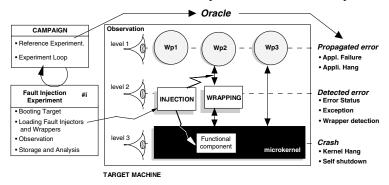

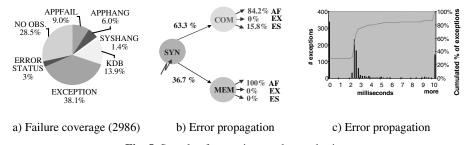

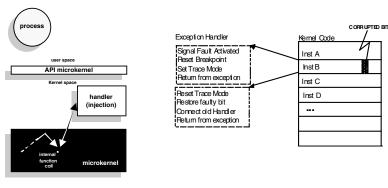

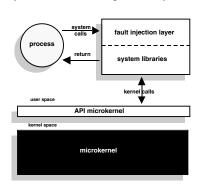

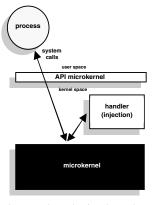

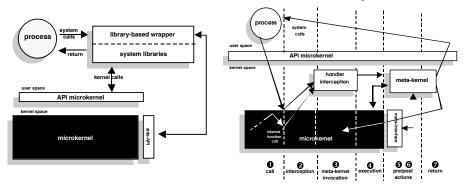

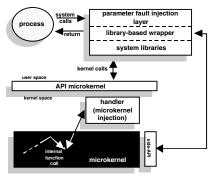

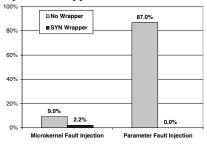

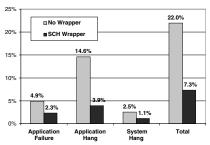

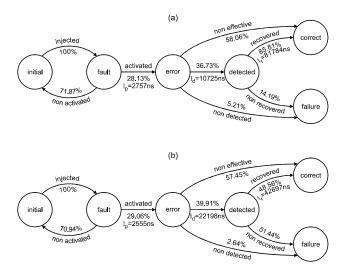

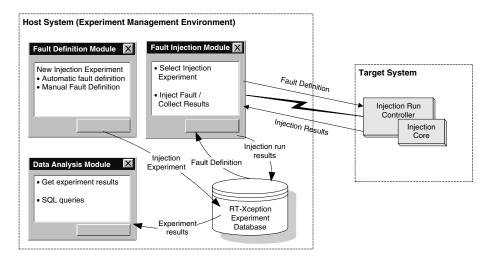

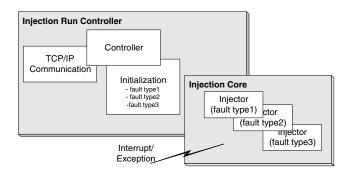

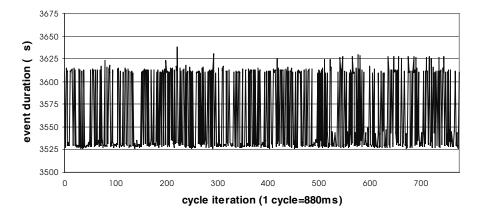

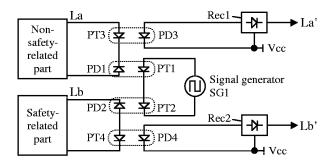

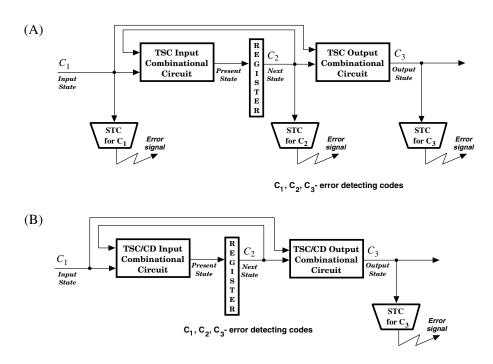

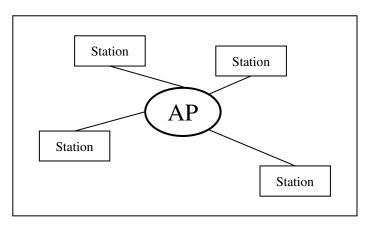

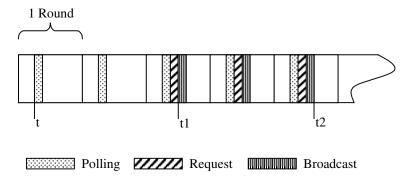

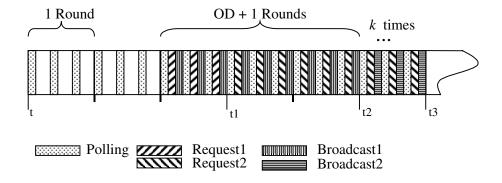

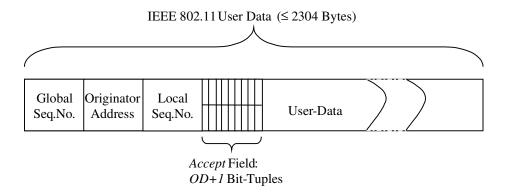

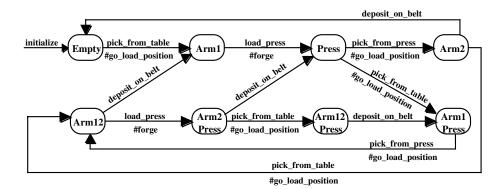

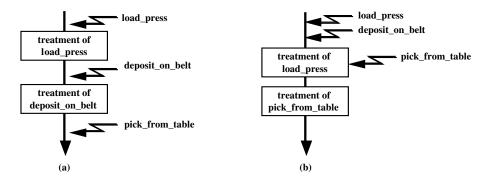

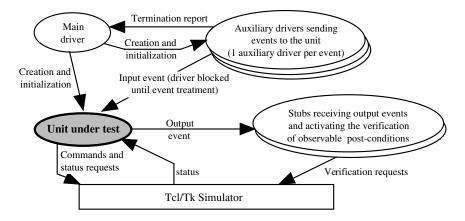

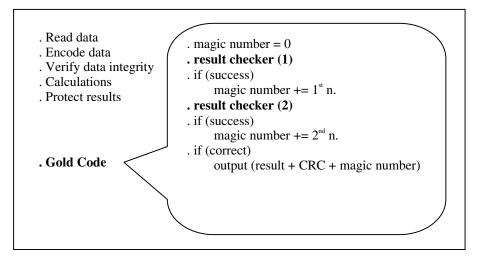

- M. Smotherman and K. Zemoudeh, "A Non-Homogeneous Markov Model for Phased-Mission Reliability Analysis," IEEE Transactions on Reliability, Vol. 38, pp. 585-590, 1989.